George Toms synthesis Home

George Toms synthesis Home

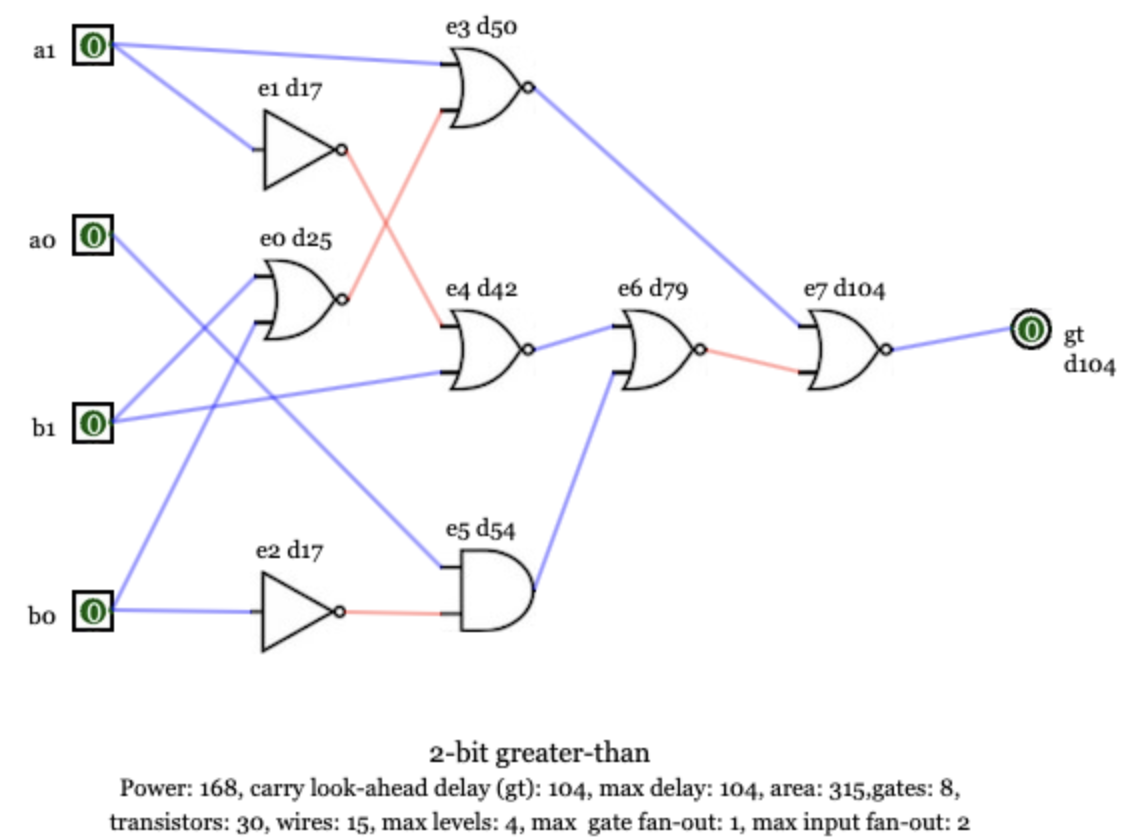

2-bit greater-than circuit

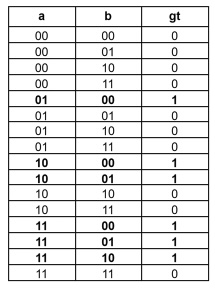

The greater-than circuit compares two inputs, a and b, and asserts an output when a is greater than b.Truth table for a 2-bit greater-than circuit

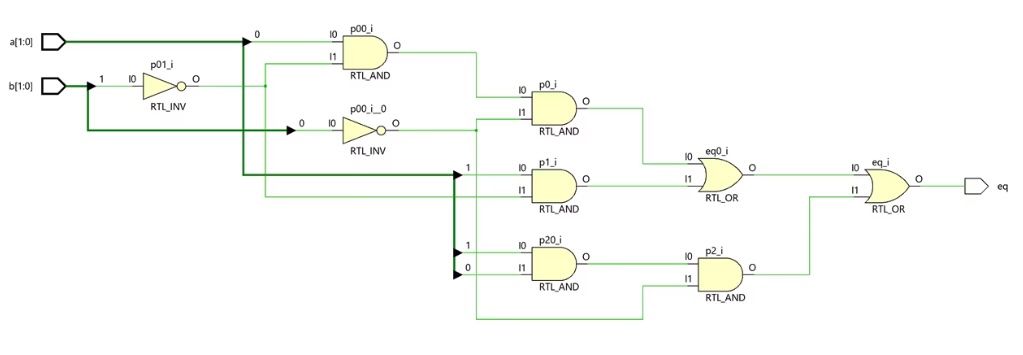

2-bit greater-than circuit designed by AMD XILINX Vivado Tool. Power: 198, area: 510, 173 ps maximum delay, max. levels: 5, max gate fan-out: 2, max input fan-out: 4, 9 gates, 58 transistors, 17 wiress

Source: SystemVerilog Study Notes. Gate-Level Combinational Circuit

Our results

We used this gate setting.Here is our Truth Table.

Here are all our 45 results.

Our version:

Our version of 2-bit greater-than circuit outperforms the AMD XILINX Vivado version in several key areas:

- it reduces power consumption by 1.17 times,

- improves delay (performance) by 1.66 times,

- decreases area requirements by 1.62 times,

- cuts gate count by 1.25 times,

- reduces transistor count by 1.93 times,

- and lowers wire usage by 1.13 times.