George Toms synthesis Home

George Toms synthesis Home

7 segment hexadecimal decoder

We found many implementations, but we think that our versions will overperform any other (please send us your version, if it is better)!

We found following good implementations to compare:

1. Power: 772, area: 1320, 333 ps maximum delay, max. levels: 8, max fan-out: 4, 24 gates, 144 transistors, 55 wires

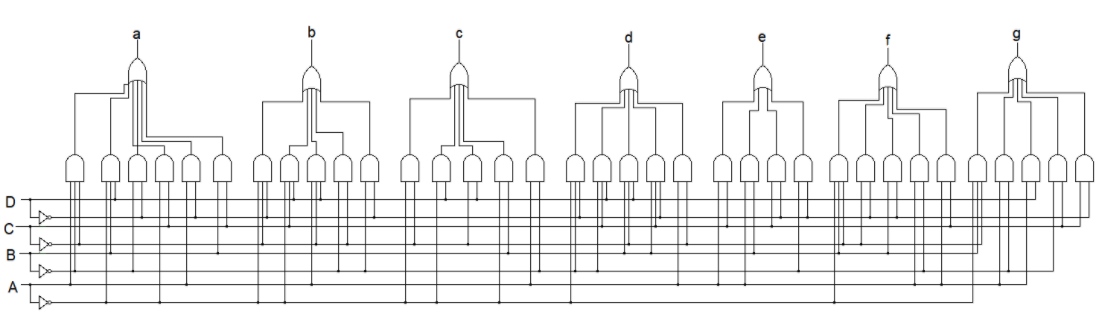

2. 46 gates, 324 transistors, 120 wires, 150 ps maximum delay, max. levels 3, max fan-out: 11:

Two gate-level netlists designed by Logic Friday system:

3. Power: 865, area: 1835, 507 ps maximum delay, max. levels: 16, max fan-out: 7, 38 gates, 170 transistors, 87 wires

4. Power: 1200, area: 2190, 391 ps maximum delay, max. levels: 12, max fan-out: 8, 48 gates, 216 transistors, 112 wires

Our results

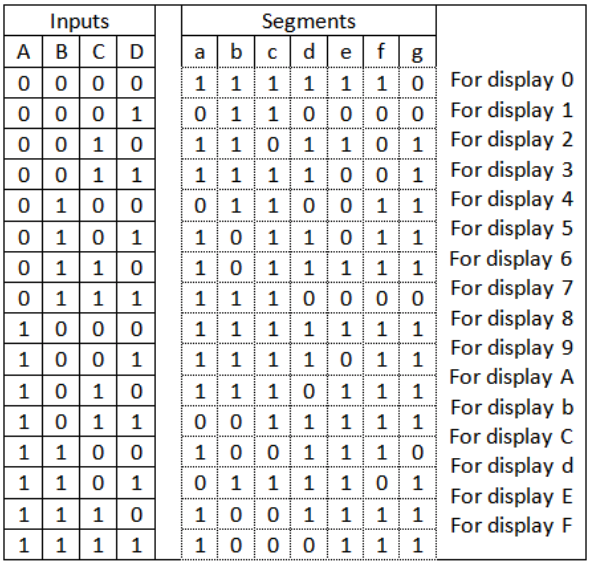

We used this gate setting.Our Truth Table.

Here are all our 733 results.

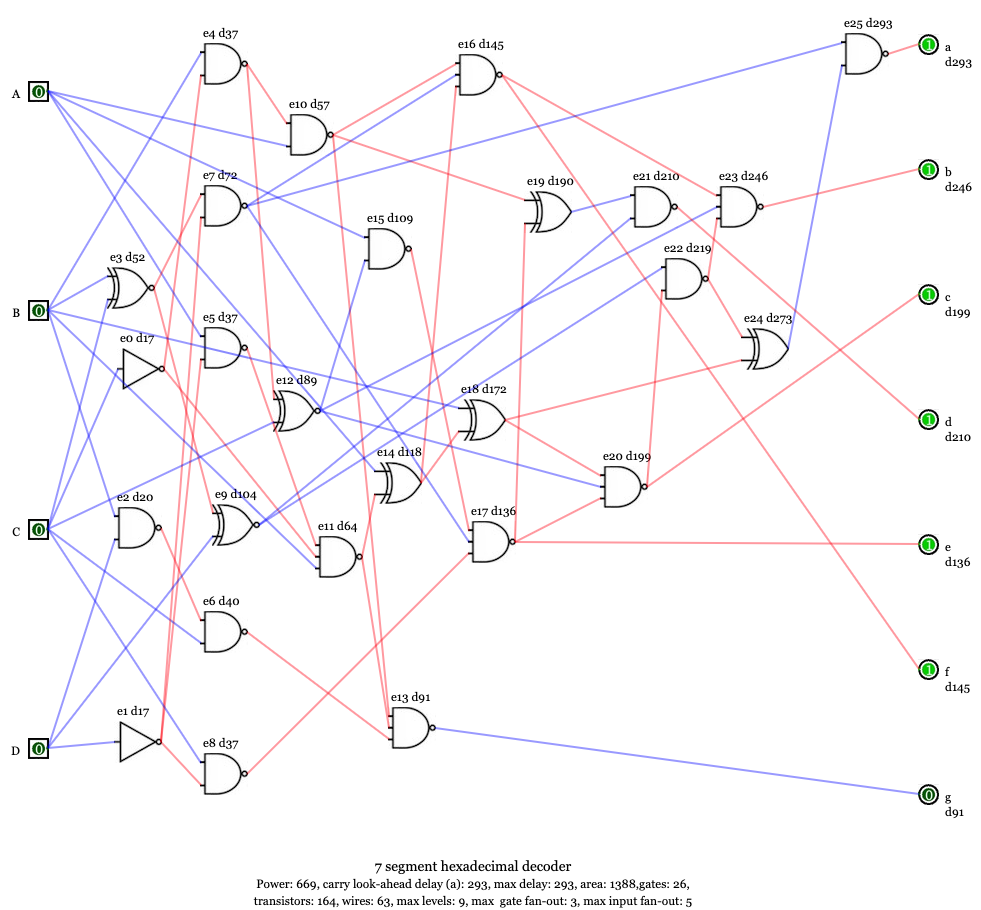

Version 1. Minimum area:

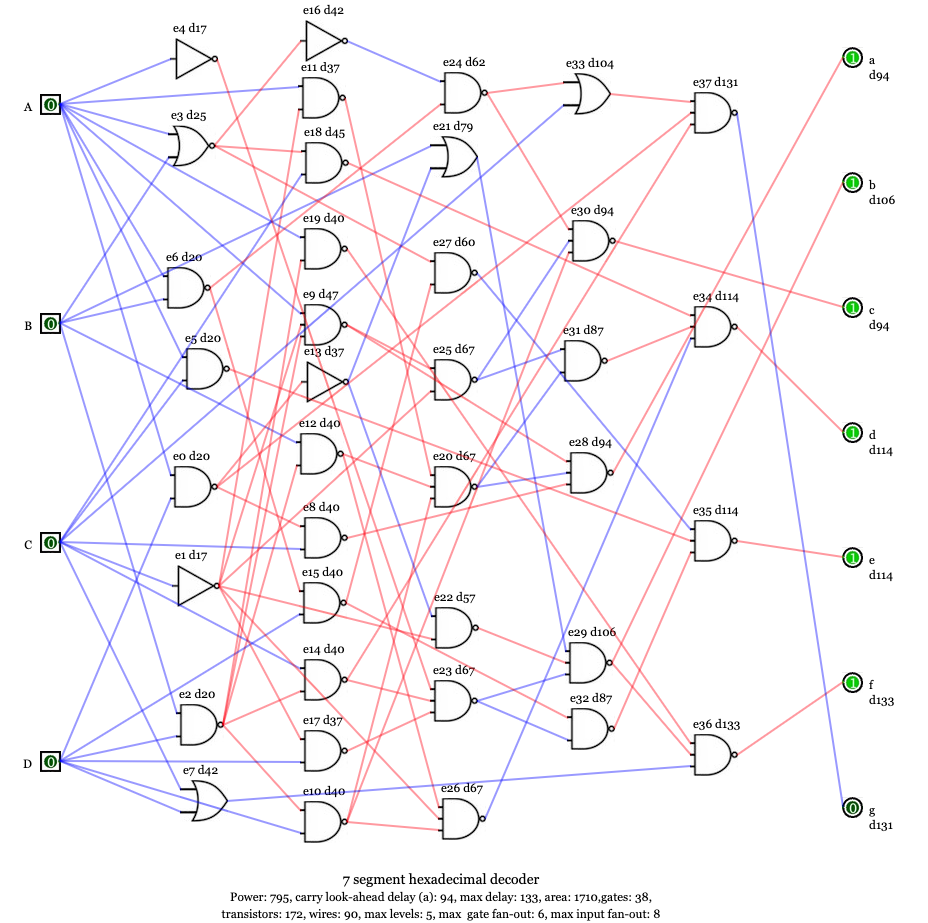

Version2. Fastest version:

Version 3. Minimum power: