George Toms synthesis Home

George Toms synthesis Home

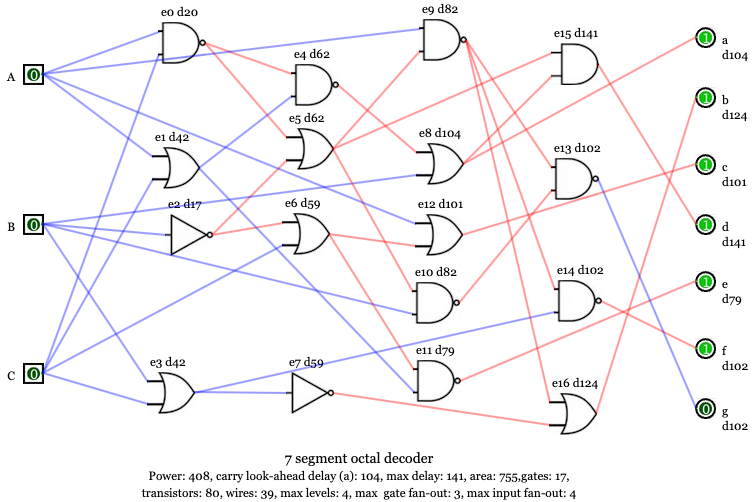

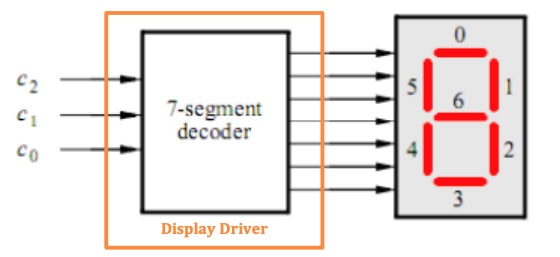

7 segment octal decoder

We found many implementations, but we think that our versions will overperform any other (please send us your version, if it is better)!

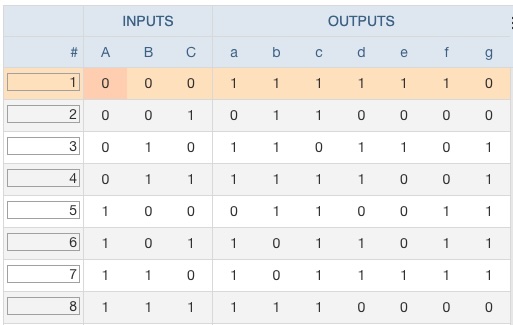

Truth table

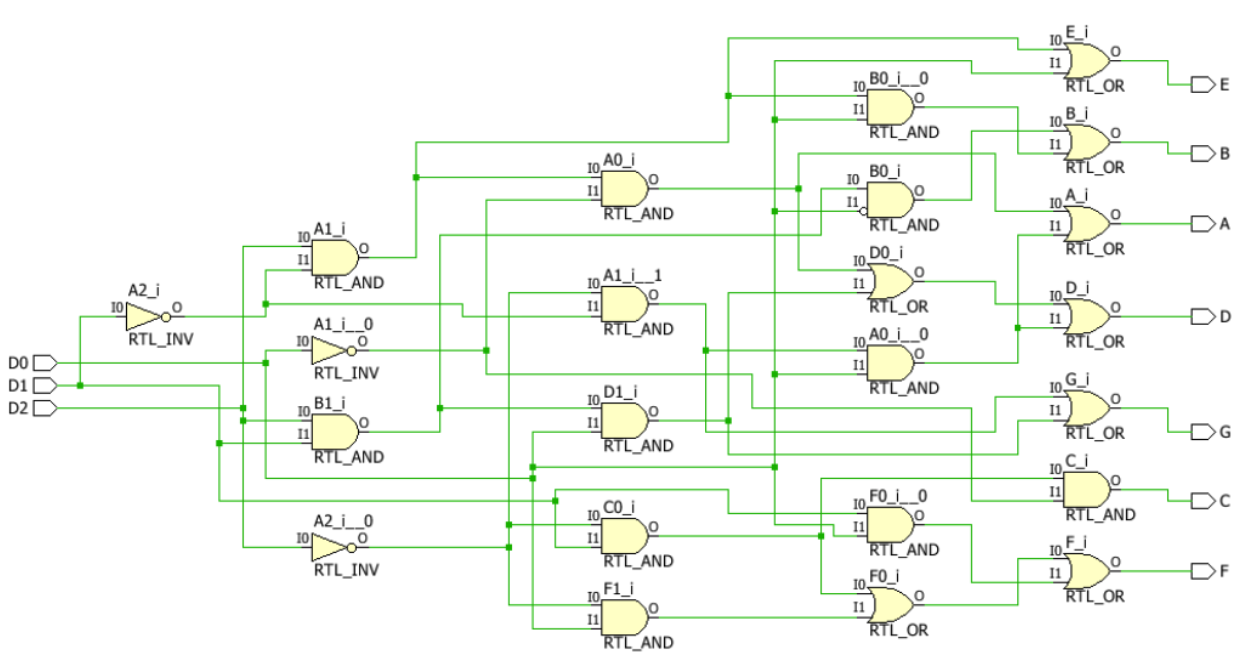

Gate-level netlist designed by Vivado Design Suite (Developer: Xilinx, AMD):

Power: 581, area: 1100, maximum delay : 175, gates: 23, transistors: 126, wires: 50, max. levels: 5, max gate fan-out: 3, max input fan-out: 8

Our results

We used this gate setting.Here is our Truth Table.

Here are all our 322 results.

Our schematic version:

Our version of 7 segment octal decoder circuit outperforms the Vivado Design Suite version in several key areas:

- it reduces power consumption by 1.42 times,

- improves delay (performance) by 1.24 times,

- decreases area requirements by 1.45 times,

- cuts gate count by 1.35 times,

- reduces transistor count by 1.57 times,

- and lowers wire usage by 1.28 times.