George Toms synthesis Home

George Toms synthesis Home

New Challenges for the FPGA Logic Synthesis Stage

(Int to float converter)

As modern FPGAs continue to scale,

wire area and wire delay are becoming more dominant factors than logic-related delays.

Both wire quantity and wire length contribute significantly to the overall wire area.Swapping connections so that a LUT-6 is driven by other LUT outputs instead of FPGA primary inputs generally is preferable — because those new sources are usually closer and lighter to route than long, high-fan-out input nets.

Additionally, larger LUTs (with more inputs) lead to higher delay and greater power consumption. Reducing the number of LUT inputs by just one can lower the power usage of that LUT by more than 16%.

High fan-out of circuit inputs—along with the resulting need for buffering and replication—further increases both power consumption and delay.

GT Synthesis technology addresses all these challenges directly during the logic synthesis stage.

However, current evaluations of LUT-6 mapped benchmarks typically rely on only two parameters:

-

The number of LUTs

-

The number of logic (LUT) levels

-

Total number of wires

-

Number of input-connected wires

-

Total number of LUT input pins used

-

Maximum fan-out for circuit inputs and LUT outputs

Case Study: Int to float converter (EPFL Benchmark 2024)

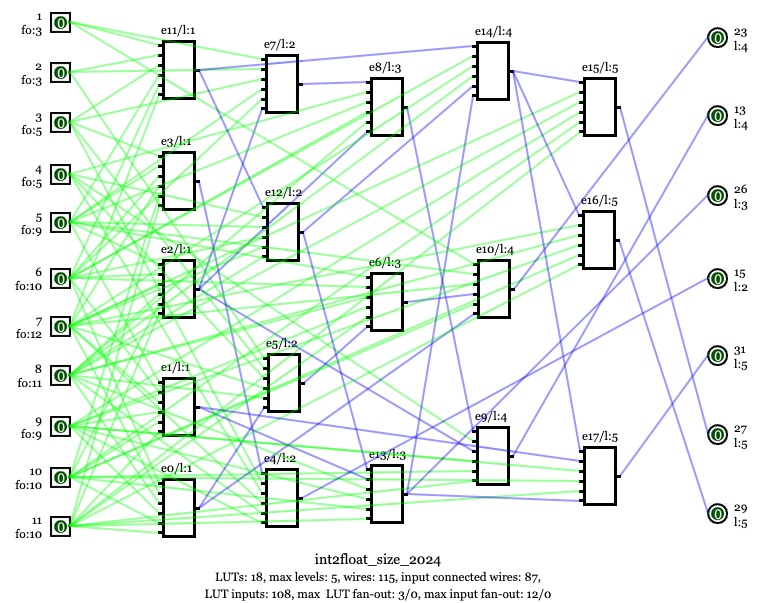

Below is an example comparing the best published Int to float converter design (int2float_size_2024) from the IPFL benchmark 2024 with GTs’ improved versions.Original (int2float_size_2024):

-

LUT count: 18

-

Logic level count: 5

-

Total LUT input pins used: 108

-

Total wire count: 115

-

Maximum input fan-out: 12

-

Input-connected wires count: 87

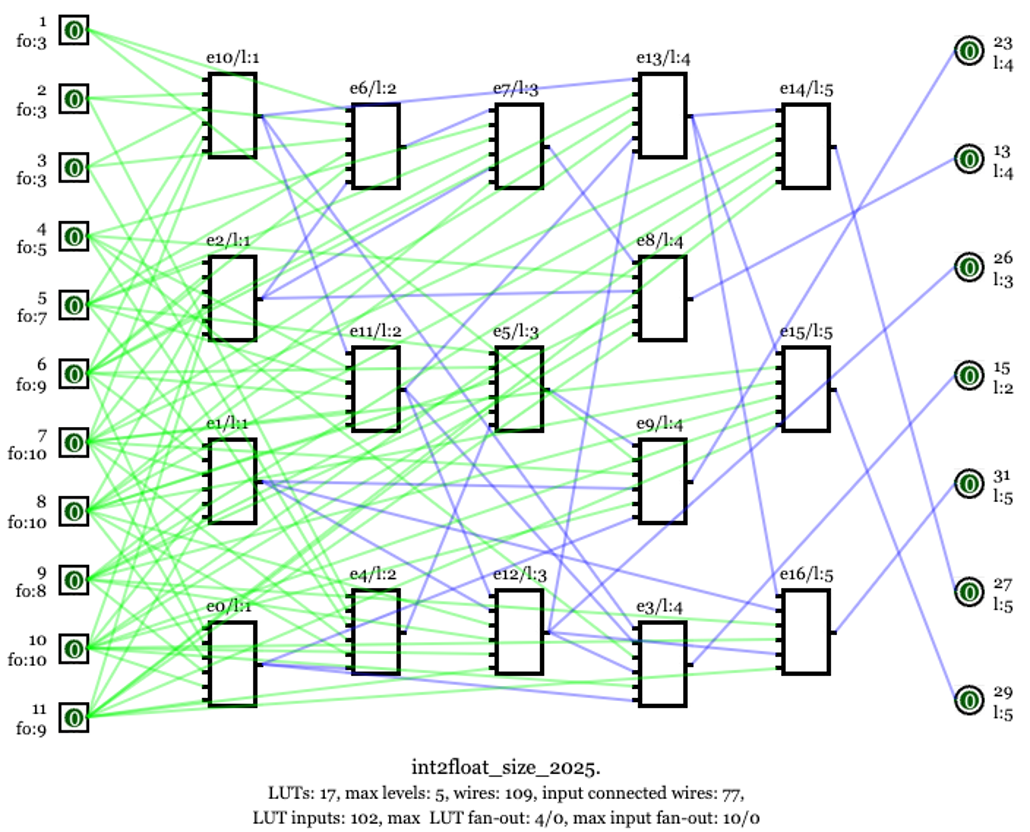

GTs version (int2float_size_2025):

This version "i2f_size_2025" has the following characteristics:

-

LUT count: 17

-

Logic level count: 5

-

Total LUT input pins used: 102

-

Total wire count: 109

-

Maximum input fan-out: 10

-

Input-connected wires count: 77

Performance Gains:

-

Reduces LUT count by 1.06× (5.6%),

-

Reduces LUT

input pins count by 1.058× (5.5%),

-

Decreases wire

count by 1.055× (5.2%),

-

Cuts the circuit input buffer

count from 2 to 0 (max input fan-out from 12 to 10),

-

Lowers the usage of input-connected

(longest) wires by 1.13× (11%).

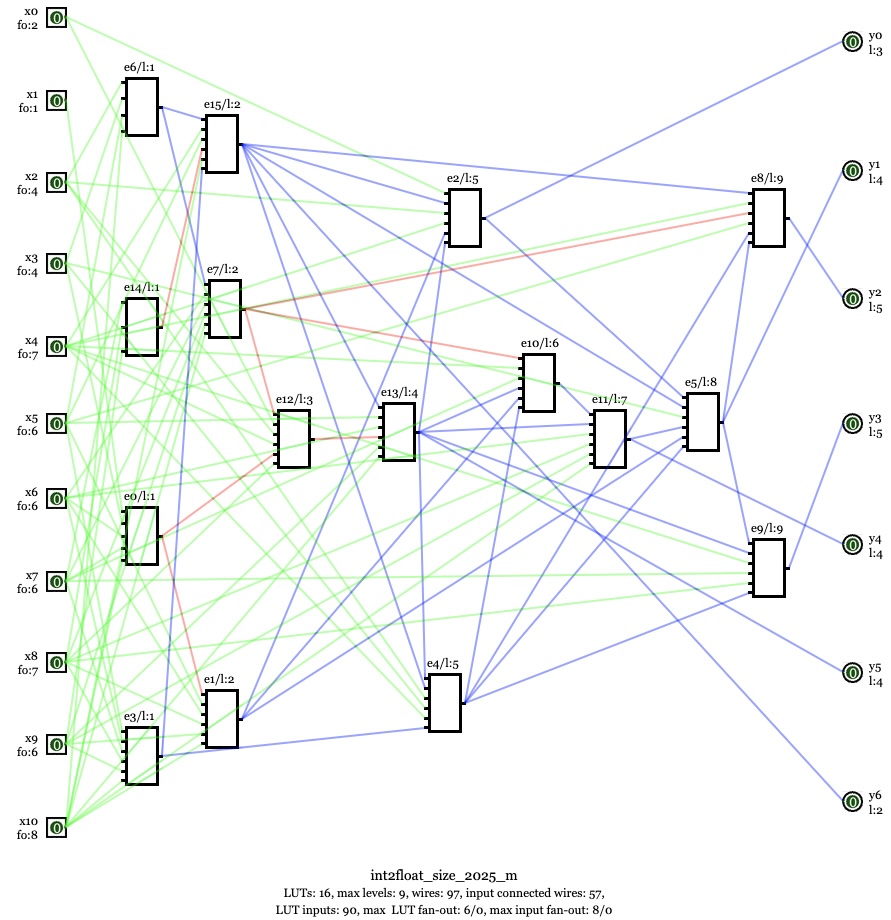

Further Optimization (int2float_size_2025_m):

-

LUT count: 16

-

Logic level count: 9

-

Total LUT input pins used: 90

-

Total wire count: 97

-

Maximum input fan-out: 8

-

Input-connected wires count: 57

Results:

-

Reduces LUT count by 1.12× (11%),

-

Reduces LUT

input pins count by 1.2× (16%),

-

Decreases wire

count by 1.18× (15%),

-

Cuts the circuit input buffer

count from 2 to 0 (max input fan-out from 12 to 8),

-

Lowers the usage of input-connected

(longest) wires by 1.52× (34%).