George Toms synthesis

George Toms synthesis

The initial stride towards the automation of logic minimization took place with the introduction of the Quine–McCluskey algorithm, a milestone that could be implemented on computers. This exact minimization technique introduced the concepts of prime implicants and minimum cost covers, forming the foundation for two-level minimization.

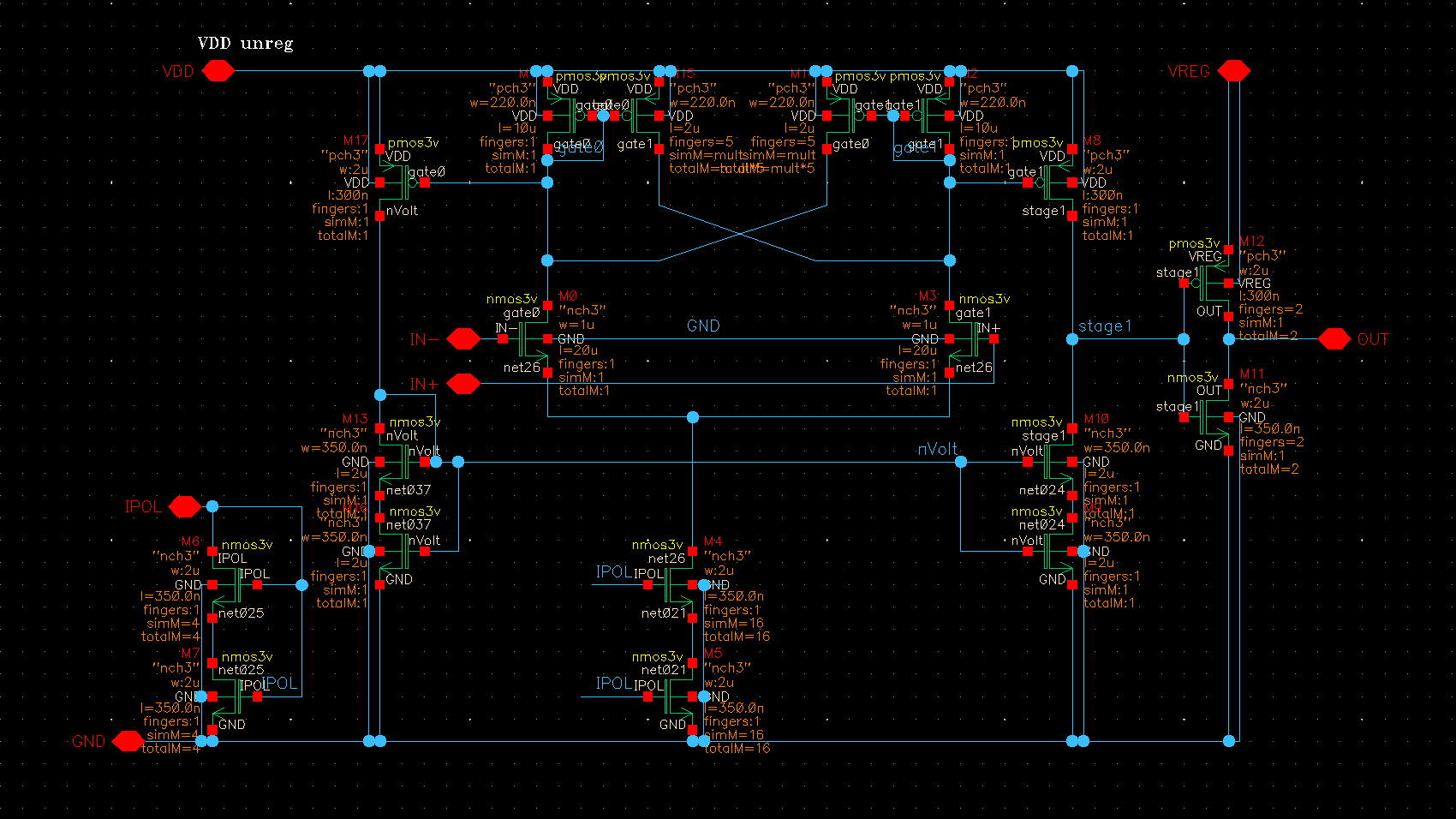

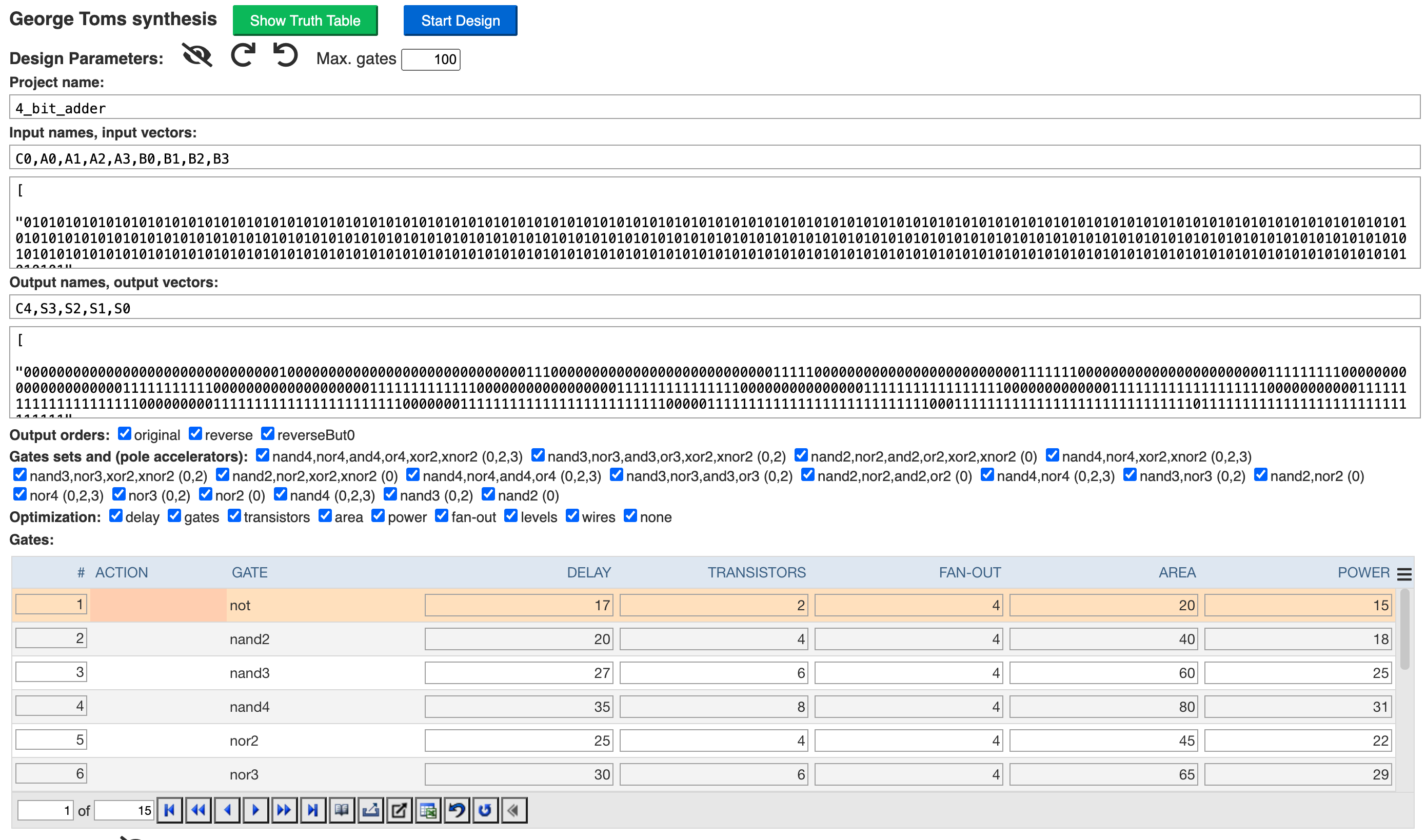

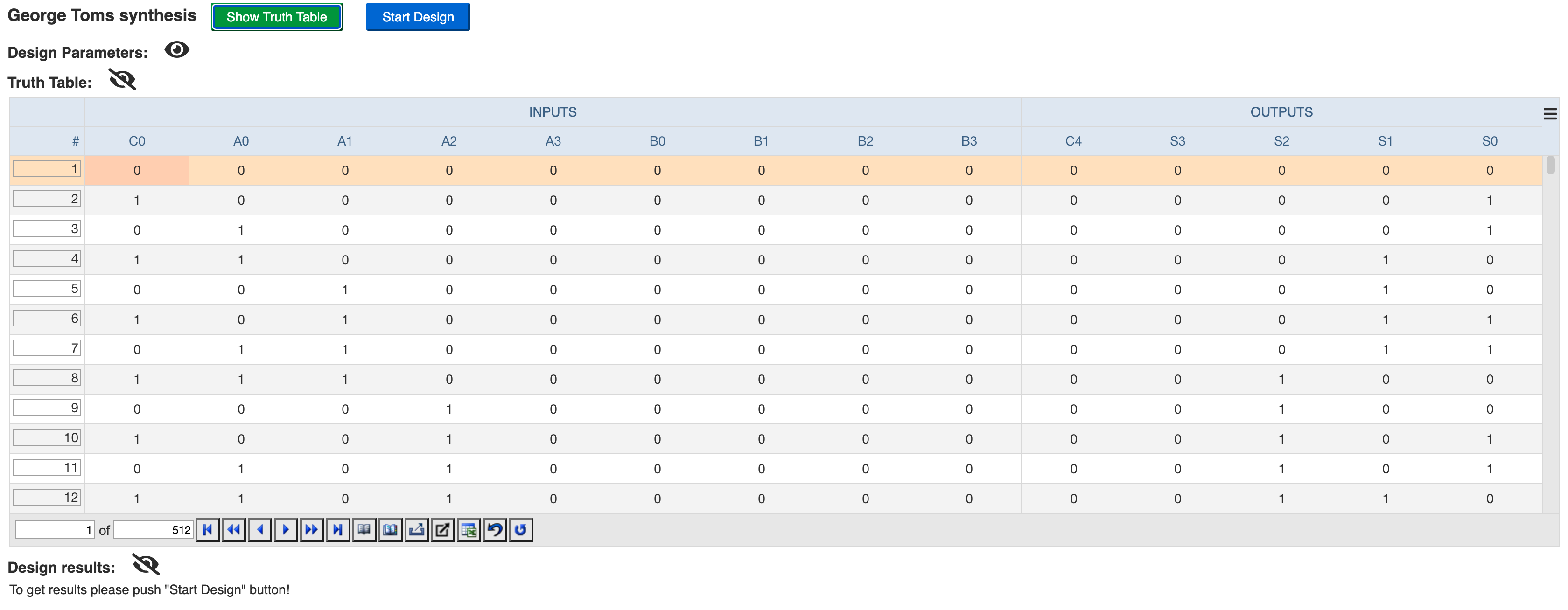

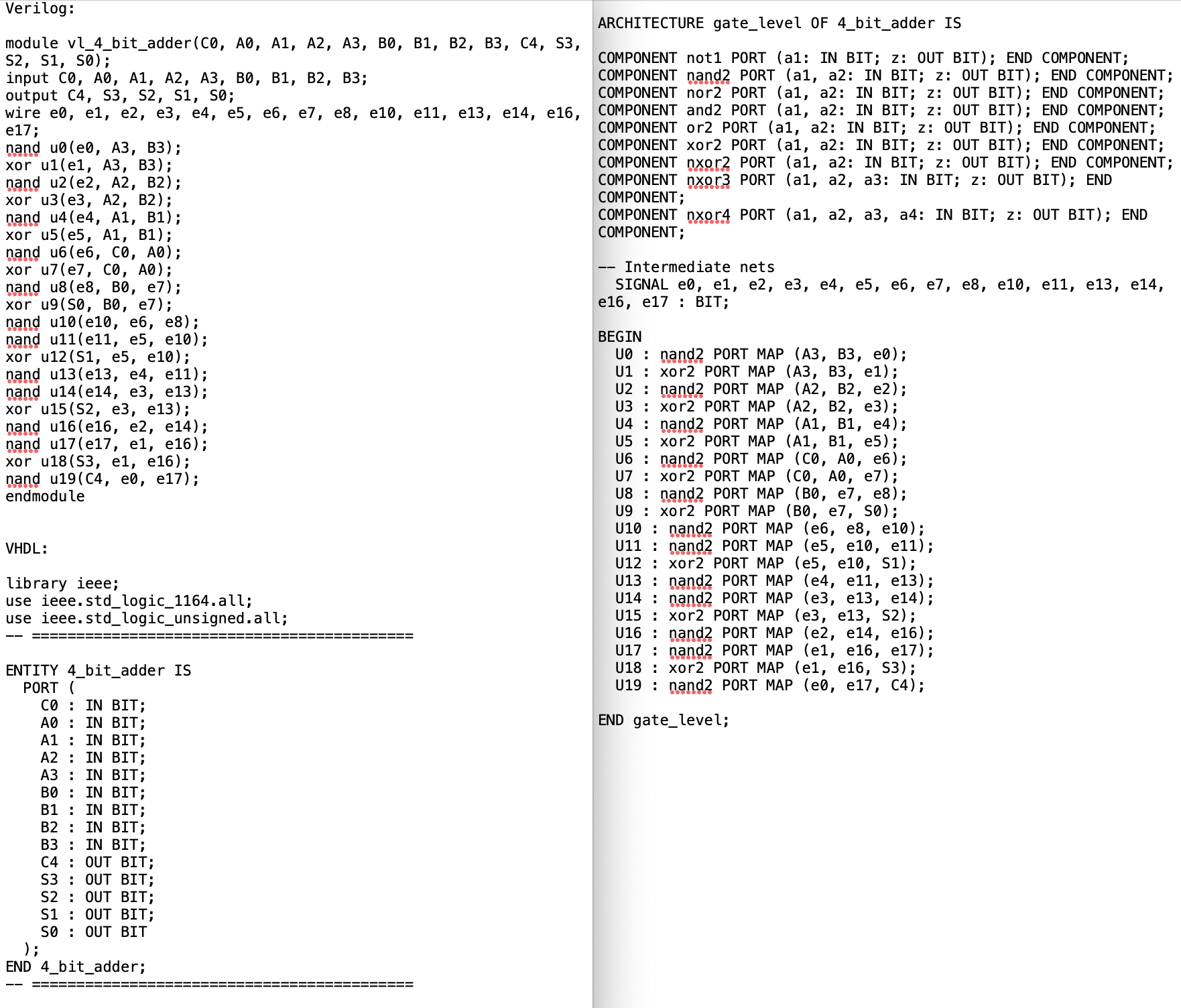

Our pioneering contribution to this field lies in the complete implementation of George Toms synthesis (GTs), a cutting-edge and profoundly transformative Combinatorial Digital Logic Synthesis technology. Setting itself apart from established methodologies centered on Boolean function optimization, GTs stands as a bold paradigm shift, heralding a new era in the domain.

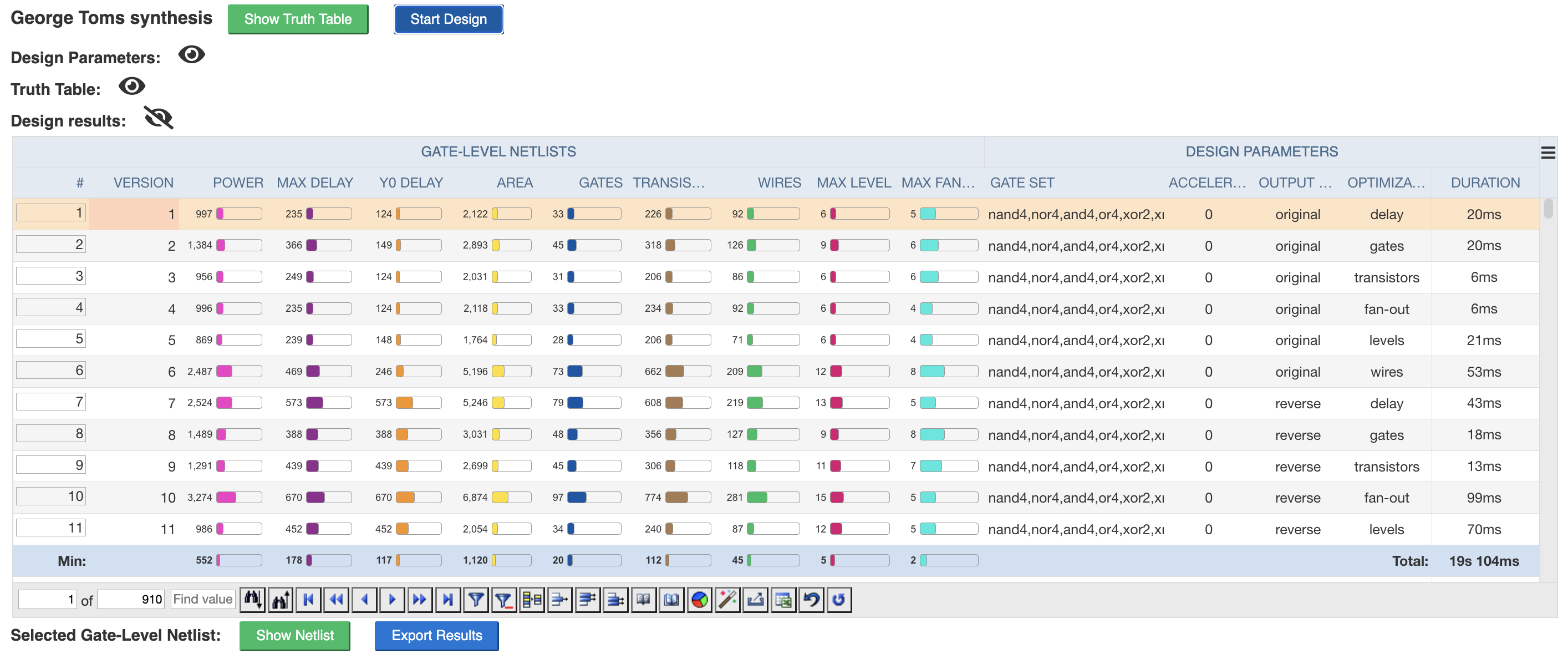

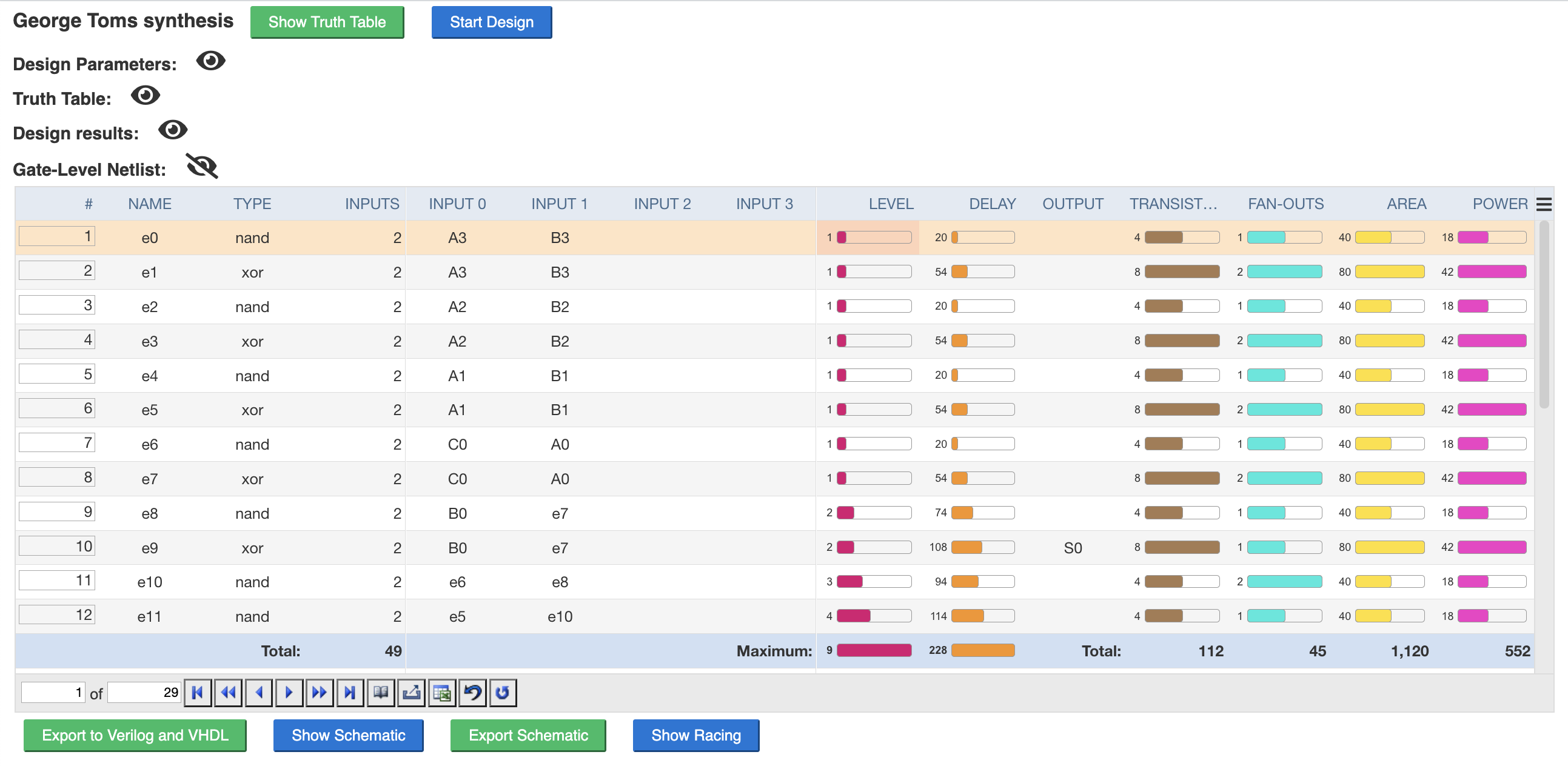

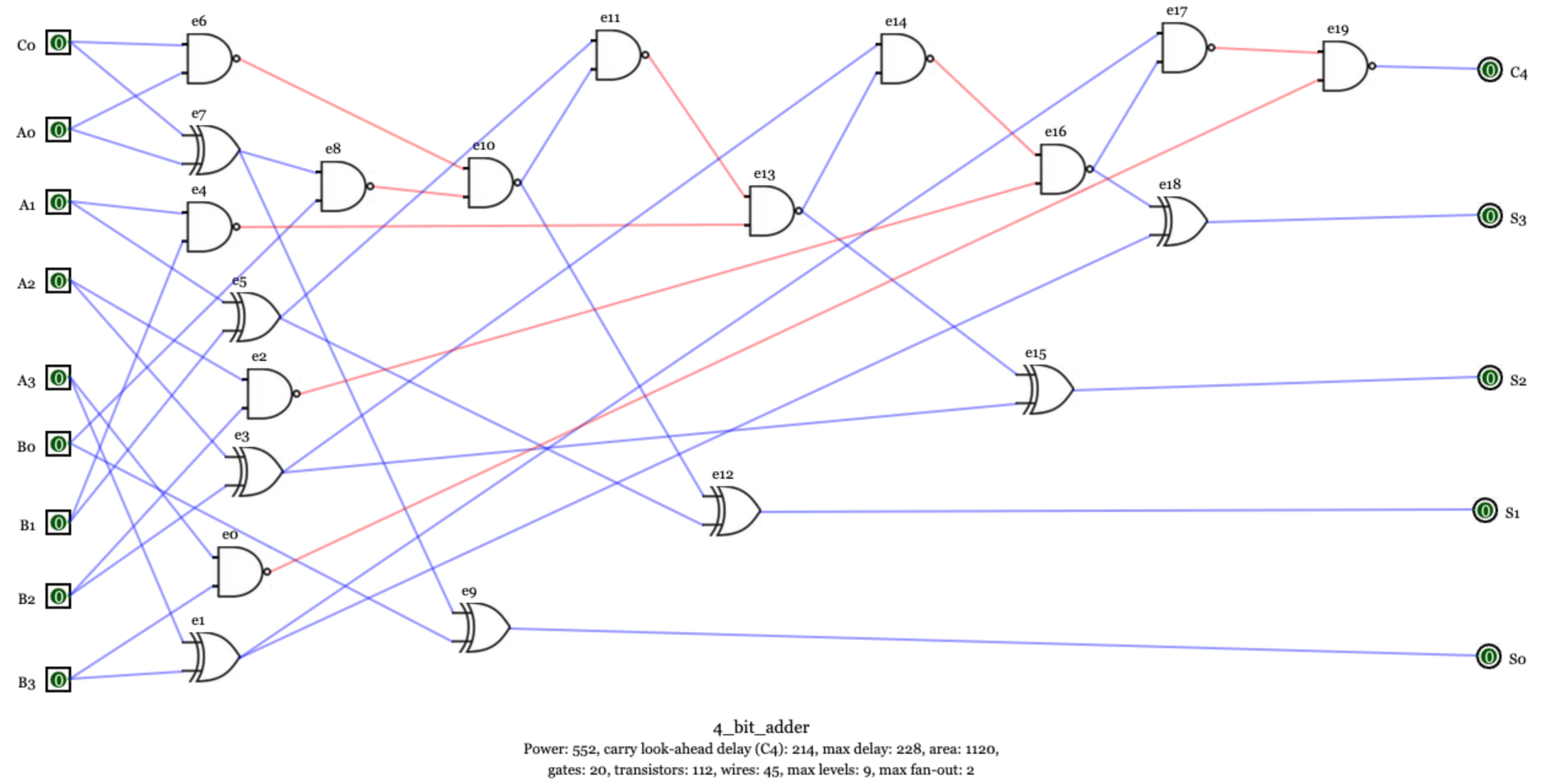

GTs surpasses all existing logic synthesis technologies in terms of the quality of results achieved across various parameters, including performance (delay), power consumption, total area, gate count, transistor count, wire/connection count (total number of gate inputs), maximum gate output fan-outs, and maximum gate level. Its cutting-edge algorithms ensure superior performance and efficiency, making it the preferred choice for designers seeking optimal solutions for their digital logic designs.

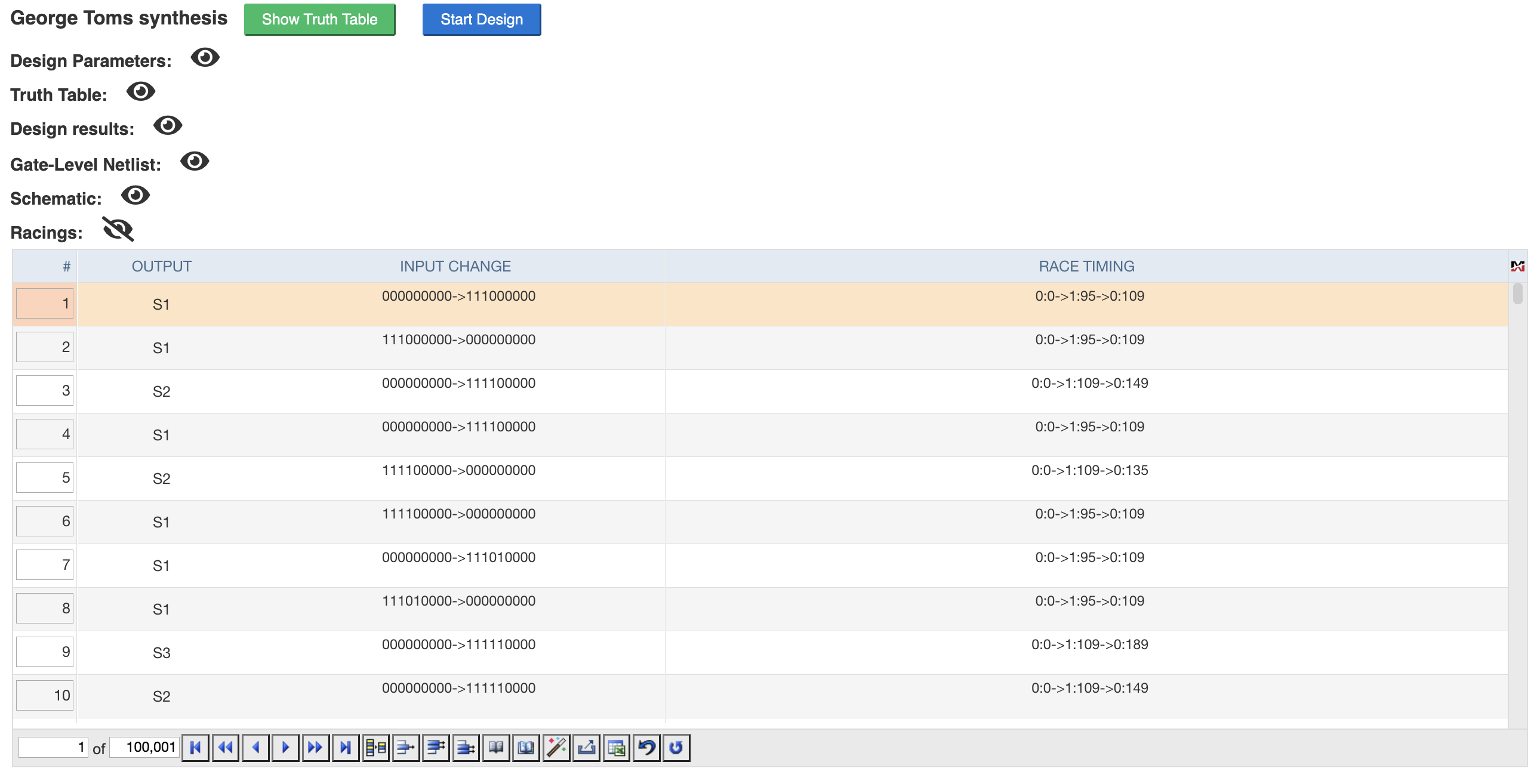

Additionally, our innovations encompass a new generation of interfaces and tools for net-list visualization, simulation, race analysis, among others, ushering in a new era of ASIC design.

Notably, GTs operates seamlessly on regular computers, laptops, or tablets within any browser environment, representing a 'quantum leap' in how web browser users visualize and interact with truth tables, gate libraries, hundreds of ready-to-go netlists, detailed netlist information, potential race conditions, and schematics with timing information and simulation capabilities.

In addition, GTs prioritizes maximum data security by enabling all required synthesis data, including truth tables, gate libraries, constraints, and synthesis results, to be stored locally.

It's crucial to emphasize that GT synthesis technology stands unrivaled in the current global landscape, surpassing both quality and speed compared to all existing similar technologies. This highlights GT's outstanding performance, confirming its position as the forefront of logic synthesis advancements in the industry!

In just one day, we can demonstrate our ability to enhance the performance of any combinational circuit developed using existing technologies across all parameters. The degree of improvement depends on the complexity of the ASIC: the more intricate the ASIC, the greater the enhancements we guarantee.

In the Proof of concept section, you'll find a comparison of our technology's results with Gate-Level Netlists and FPGA created by leading professionals worldwide:

- New Challenges for the FPGA Logic Synthesis Stage (Alu control unit)

- New Challenges for the FPGA Logic Synthesis Stage (Int to float converter)

- GTs vs Vivado: 7 segment octal decoder

- GTs vs Vivado: 2-bit greater-than circuit

Built on current standard web technologies—JavaScript, HTML, and CSS—our technology incorporates Megadatab Web technology (MDW) in our interface. This enables us to create exceptional data visualizations and effortlessly process synthesis results. No additional hardware, programming languages, plugins, or other resources are required.

GT Synthesis represents a 'quantum leap' in how Web Browser users can swiftly and efficiently design Gate-Level Netlists from truth tables.

This technology dramatically streamlines and optimizes the entire process of Combinational Logic Synthesis.

It is better to try something once than to hear about it a thousand times.

Please try...

Please try...

Proof of Concept

Please review GT synthesis circuit examples:

When Will It Be Available?

GT synthesis is fully implemented, debugged, and being tested on a

variety of circuits.It is easy to use:

- Compatible and interoperable with all standard browsers (e.g. Chrome, Firefox, Edge, Safari, Opera, Vivaldi, Internet, etc.)

- Requires no additional client-side software or plug-ins

Contact Us

- USA: +1 (858) 699-8940

- n@gtsynt.com

In most cases, we can solve your problems promptly and efficiently.